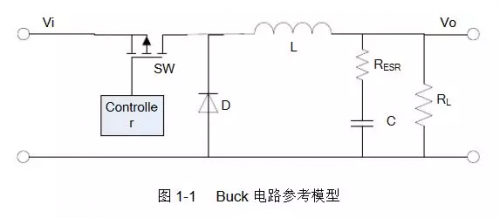

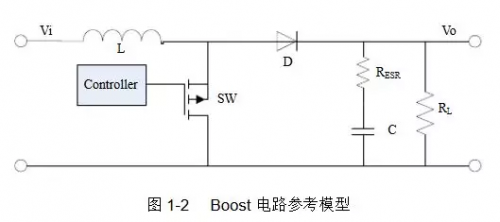

開關電源的主要部件包括:輸入源、開關管,、儲能電感,、控制電路、二極管,、負載和輸出電容,。目前絕大部分半導體廠商會將開關管、控制電路、二極管集成到一顆CMOS/Bipolar工藝的電源管理IC中,,極大簡化了外部電路,。

開關電源的主要部件包括:輸入源、開關管,、儲能電感,、控制電路、二極管,、負載和輸出電容,。目前絕大部分半導體廠商會將開關管、控制電路、二極管集成到一顆CMOS/Bipolar工藝的電源管理IC中,,極大簡化了外部電路,。

其中儲能電感作為開關電源的一個關鍵器件,對電源性能的好壞有重要作用,,同時也是產(chǎn)品設計工程師重點關注和調(diào)試的對象,。隨著像手機、PMP,、數(shù)據(jù)卡為代表的消費類電子設備的尺寸正朝著輕,、薄、小巧,、時尚的趨勢發(fā)展,,而這正與產(chǎn)品性能越強所要的更大容量、更大尺寸的電感和電容矛盾,。因此,,如何在保證產(chǎn)品性能的前提下,減小開關電源電感的尺寸(所占據(jù)的PCB面積和高度)是本文要討論的一個重要命題,,設計者將不得不在電路性能和電感參數(shù)間進行折中(Tradeoff),。

任何事物都具有兩面性,開關電源也不例外,。壞的PCB布局布線設計不但會降低開關電源的性能,,更會強化EMC、EMI,、地彈(grounding)等,。在對開關電源進行布局布線時應注意的問題和遵循的原則也是本文要討論的另一重要命題。

一 開關電源占空比D,、電感值L,、效率η公式推導

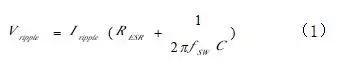

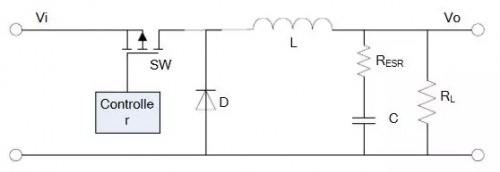

Buck型和Boost型開關電源具有不同的拓撲結構,本文將使用如圖1-1,、1-2所示的電路參考模型[1]:

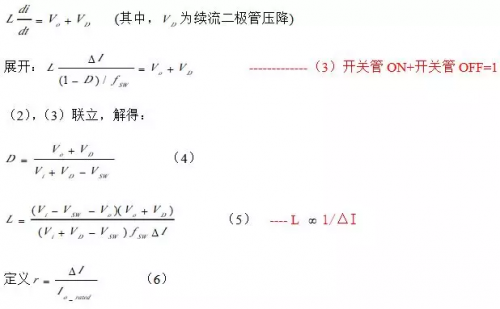

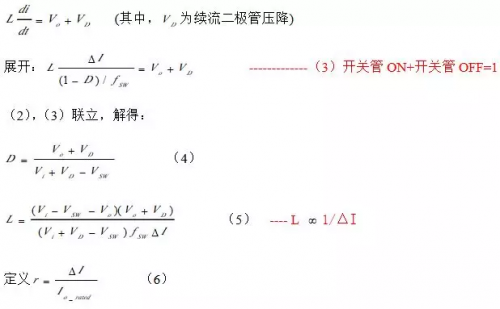

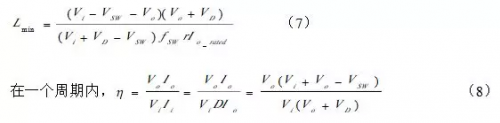

所以,,

展開:

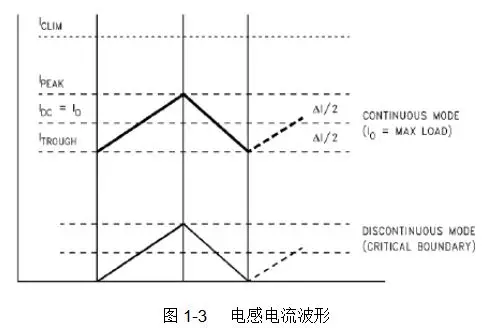

在一個連續(xù)模式的周期內(nèi),,開關管打開,電感放電,,根據(jù)基爾霍夫定律有:

此值一般為常量,。從(5)式可以得到:電感值越大,I?就越小,,因此r就越小,。但這往往導致需要一個很大的電感才能辦到,所以絕大部分的Buck型開關電源選擇r值在0.25~0.5之間,。

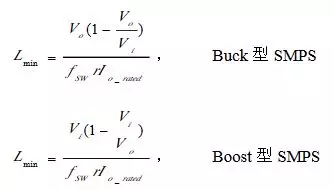

將(6)代入(5)式,,得到:

從(4)式可以看到,,占空比只與V(i),、V(o)、V(sw)和V(D)相關,,可以很容易搭建電路計算出D,,這也是開關電源控制器的核心電路之一,但對開關電源的應用者來說,,我們可以不關心,。

從(8)式可以看出,開關電源的效率也只與V(i),、V(o),、V(sw)和V(D)相關,。事實上V(sw)和V(D)是開關頻率f(sw)的函數(shù),所以也是f(sw)的函數(shù),,但并不能保證f(sw)越高,,就越高。

而對于一個給定的Buck型開關電源,,其SWf是確定的,,所以也就是定值,尤其在忽略V(sw)和V(D)后,,值為1,。很明顯這與實際情況不符,根本原因就在于“參考模型假定儲能電感為理想電感”,。

把(5)式代入(1)式,,可以得到:

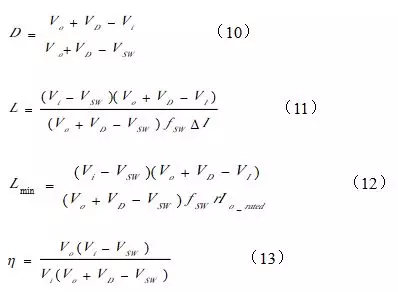

同理,可以推導出了Boost型開關電源的D,、L,、minL,如下所示:

公式(7),、(12)分別給出了通用的Buck和Boost型開關電源的電感最小值選取公式,。

對像手機、PMP,、數(shù)據(jù)卡這類的消費類電子用到的低功率開關電源,,V(sw)和V(D)都在0.1V~0.3V之間,因此可對公式(7),、(12)進行簡化,,得到: